# Low-Voltage Operation of ZrO<sub>2</sub>-Gated n-Type Thin-Film Transistors Based on a Channel Formed by Hybrid Phases of SnO and SnO<sub>2</sub>

Hsin-Chueh Chu, Yung-Shao Shen, Ching-Heng Hsieh, Jia-Hong Huang, and Yung-Hsien Wu\*

Department of Engineering and System Science, National Tsing Hua University, Hsinchu, Taiwan

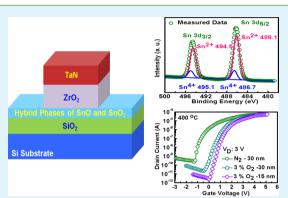

**ABSTRACT:** With SnO typically regarded as a p-type oxide semiconductor, an oxide semiconductor formed by hybrid phases of mainly SnO and a small amount of SnO<sub>2</sub> with an average [O]/[Sn] ratio of 1.1 was investigated as a channel material for n-type thin-film transistors (TFTs). Furthermore, an appropriate number of oxygen vacancies were introduced into the oxide during annealing at 400 °C in ambient N<sub>2</sub>, making both SnO and SnO<sub>2</sub> favorable for current conduction. By using high- $\kappa$  ZrO<sub>2</sub> with a capacitance equivalent thickness of 13.5 nm as the gate dielectric, the TFTs processed at 400 °C demonstrated a steep subthreshold swing (SS) of 0.21 V/dec, and this can be ascribed to the large gate capacitance along with a low interface trap density ( $D_{it}$ ) value of 5.16 × 10<sup>11</sup> cm<sup>-2</sup> eV<sup>-1</sup>. In addition, the TFTs exhibit a relatively high electron mobility of 7.84 cm<sup>2</sup>/V·s, high ON/OFF current ratios of up to 2.6 × 10<sup>5</sup> and a large sta lackness memory is a large star and a steep subtreshole such a steep such as the provide the large star and a steep for the large star and a steep such a steep such as the steep such as the steep step of 5.16 × 10<sup>11</sup> cm<sup>-2</sup> eV<sup>-1</sup>. In addition, the TFTs exhibit a relatively high

ACS APPLIED MATERIALS

& INTERFACES

Letter

www.acsami.org

$2.5 \times 10^5$ , and a low gate leakage current at a low operation voltage of 3 V. The TFTs also prove its high reliability performance by showing negligible degradation of SS and threshold voltage ( $V_T$ ) against high field stress (-10 MV/cm). When 3% oxygen annealing is combined with a thinner channel thickness, TFTs with even higher  $I_{ON}/I_{OFF}$  ratios exceeding 10<sup>7</sup> can also be obtained. With these promising characteristics, the overall performance of the TFTs displays competitive advantages compared with other n-type TFTs formed on binary or even some multicomponent oxide semiconductors and paves a promising and economic avenue to implement an n-type oxide semiconductor without doping for production-worthy TFT technology. Most importantly, when combined with the typical SnO-based p-type oxide semiconductor, it would usher in a new era in achieving high-performance complementary metal oxide semiconductor circuits by using the same SnO-based oxide semiconductor.

KEYWORDS: SnO<sub>2</sub>/SnO hybrid channel, n-type TFTs, mobility, subthreshold swing, ZrO<sub>2</sub>, CET, interface trap density, reliability

$\Lambda$  ith the advent of a novel oxide semiconductor for an active channel layer of thin-film transistors (TFTs), flatpanel displays are a ubiquitous commodity product representing a huge market. For an n-type oxide semiconductor, several promising materials such as InGaZnO,<sup>1,2</sup> YInZnO,<sup>3</sup> SnInZnO,<sup>4</sup> and ZrSnZnO<sup>5</sup> have been extensively studied. Although good electrical characteristics have been reported, these quaternary oxide semiconductors require rigorous control of the composition and therefore add process complexity. Moreover, most of these materials necessitate the incorporation of Ga or In, which are relatively rare on earth and result in possible material shortage. To simplify process control while maintaining a desirable electrical performance, the search for an appropriate Ga/In-free binary oxide semiconductor never stops. Since its debut in 1968, crystalline ZnO, which can be prepared by radio-frequency (RF) sputtering,<sup>6</sup> atomic layer deposition,<sup>7</sup> or pulse laser deposition,<sup>8</sup> has attracted intensive interest and demonstrated mobility higher than 20 cm<sup>2</sup>/V·s.<sup>6</sup> Unfortunately, the subthreshold swing (SS), which is crucial for device switching, is larger than 1.3 V/dec and needs further improvement. Doping ZnO with Li<sup>9</sup> or Ga<sup>10</sup> has also been explored; however, there is still room to improve the device performance. TiO<sub>x1</sub> another widely examined material, can be prepared by approaches similar to that of ZnO. However, the mobility did not exceed  $2 \text{ cm}^2/\text{V} \cdot \text{s}^{11,12}$  until 2013, in which year

an inspiring mobility higher than 20 cm²/V·s was reported by introducing specific chemical doping in crystalline TiO2.13 Nevertheless, the SS is still not steep enough and the reliability performance of gate bias stress instability is not evaluated either. Interestingly, even though SnO<sub>2</sub> was first developed in 1964, related researches on the material were scarcely found in the literature. Pure SnO<sub>2</sub> prepared by RF sputtering<sup>14</sup> (in the crystalline phase) and spray pyrolysis<sup>15</sup> (in the amorphous phase) respectively showed mobilities of 2 and 0.8 cm<sup>2</sup>/V·s along with an unsatisfactory SS, which necessitates further improvement. Furthermore, doping Sb<sup>16</sup> or Ta<sup>17</sup> into SnO<sub>2</sub> has been reported to have the capability of implementing n-type TFTs with significantly enhanced mobility. On the other hand, pure SnO in the crystalline phase, typically a p-type oxide semiconductor,<sup>18</sup> can also reveal electron transport near the conduction band minimum (CBM), and therefore SnO-based n-type TFTs were reported.<sup>19,20</sup> Unfortunately, the SnO-based n-type TFTs operate at large voltage and low mobilities of 1.4  $\times 10^{-3}$ -1.02 cm<sup>2</sup>/V·s<sup>19,20</sup> with undesirable SS. In addition, these n-type TFTs behaviors were obtained from the ambipolar

Received:April 4, 2015Accepted:July 6, 2015Published:July 6, 2015

SnO conduction property rather than pure n-type devices. Even though n-type SnO can also be achieved through extrinsic doping with Sb,<sup>21</sup> no data for TFTs were disclosed. Furthermore, for an oxide semiconductor, nevertheless, doping the impurities<sup>9,10,13,16,17,21</sup> is a viable approach to boosting the field mobility of binary oxide-based TFTs by increasing the carrier concentration; it inevitably increases process costs and complexity.

Among the aforementioned n-type binary oxide semiconductors, SnO holds great potential for future flat-panel circuits because it is one of the rare materials that possess ambipolar carrier conduction behavior, which makes it possible to realize complementary metal oxide semiconductor (CMOS) circuits by a single oxide semiconductor. This implies that row and column drivers, or other peripheral circuits, can be integrated onto a glass substrate. Although the ambipolar property is attractive for simplifying circuit design and fabrication processes, challenges include the following: (a) Hole and electron mobility should be carefully controlled in ambipolar devices to obtain balanced behavior for better CMOS performance.<sup>20</sup> (b) There is still room to enhance its electron mobility. Nevertheless, SnO opens an opportunity to realize an n-type semiconductor. If a pure n-type rather than an ambipolar semiconductor can be realized in SnO without intentional doping, it is possible to independently optimize the performance of n-type TFTs. In combination with the typically observed SnO-based p-type semiconductor, it would usher in a new era in achieving high-performance CMOS circuits by using the same oxide semiconductor, SnO. In this work, without any doping, an oxide semiconductor composed of mainly SnO with a small amount of  $SnO_2$  ([O]/[Sn] of 1.1) was proposed as the channel for electron transportation. Gated by ZrO<sub>2</sub> with a capacitance equivalent thickness (CET) of 13.5 nm, the n-type TFTs display a high electron mobility of 7.84 cm<sup>2</sup>/V·s, which outperforms undoped binary oxides such as  $TiO_{x}$ ,<sup>11,12</sup>  $SnO_{y}$ ,<sup>14,15</sup> SnO,<sup>19,20</sup> and ZnO,<sup>7,8</sup> doped binary oxides such as LiZnO,<sup>9</sup> and GaZnO,<sup>10</sup> or even InZnO-based oxides such as ZrInZnO<sup>2</sup>, TiInZnO<sup>2</sup>, and YInZnO.<sup>3</sup> In addition, prominent electrical characteristics in terms of a large ON/OFF ratio of  $2.5 \times 10^5$  and a steep SS of 0.21 V/dec, which is superior to many oxide-based TFTs,<sup>2,3,10-12,14,15,19,20</sup> are demonstrated. Good ZrO<sub>2</sub>/channel interfacial quality is also proven by a low interface trap density  $(D_{it})$  of  $5.16 \times 10^{11}$  cm<sup>-2</sup> eV<sup>-1</sup>. Furthermore, robust reliability is evidenced by the stable SS and threshold voltage  $(V_{\rm T})$  against gate bias stress. More importantly, desirable n-type TFTs can be operated at voltages as small as 3 V and implemented by a feasible and productionworthy process without doping or employing a multicomponent oxide semiconductor. Considering the overall performance, the channel material composed of hybrid phases of SnO/SnO<sub>2</sub> along with a ZrO<sub>2</sub> dielectric holds competitive advantages for TFT technology.

Silicon (Si) substrates topped by SiO<sub>2</sub> were used as the starting materials for front-gate n-type TFTs. A 30-nm-channel material was deposited on SiO<sub>2</sub> by evaporating the SnO<sub>2</sub> source at room temperature. Subsequently, thermal annealing at 400, 450, or 500 °C was carried out for 20 min in ambient N<sub>2</sub> at atmospheric pressure to form the channel material. Then, 60 nm high- $\kappa$  ZrO<sub>2</sub> was selectively deposited by e-beam evaporation as the gate dielectric. Finally, the n-type TFTs with an effective W (width)/L (length) of 120  $\mu$ m/40  $\mu$ m were completed by depositing TaN as the electrode followed by N<sub>2</sub> annealing at 300 °C. Besides electrical characterization of

current-voltage (I-V), capacitance-voltage (C-V), and conductance-voltage (G-V) measurements, the effect of gate bias stress on the electrical parameters was also evaluated. The carrier concentration of the oxide semiconductor was characterized by Hall-effect measurement. In addition, physical analysis such as ex situ X-ray diffraction (XRD) and X-ray photoelectron spectroscopy (XPS) measurement were respectively adopted for characterization of the oxide film crystallinity and bonding structure. XPS has been widely adopted in the elemental quantification,  $2^{2-24}$  and an accuracy of 5% is typically quoted for routinely performed XPS atomic concentrations in our XPS experimental equipment. The surface morphology of the channel material was characterized by atomic force microscopy (AFM) in separate experiments, while the dopant distribution across the oxide film was measured by secondaryion mass spectrometry (SIMS).

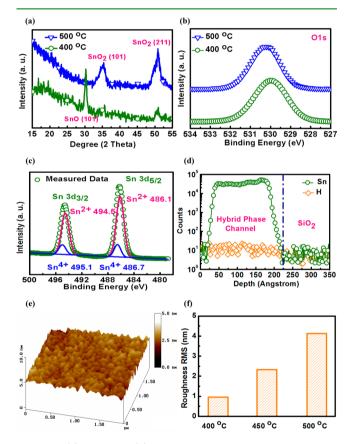

Figure 1a shows the XRD spectra for a deposited SnO film annealed at 400 and 500  $^\circ C.$  For the 400  $^\circ C$  annealed film,

**Figure 1.** (a) XRD and (b) XPS O 1s spectra for 400 and 500  $^{\circ}$ C annealed SnO films. (c) XPS Sn 3d spectrum and deconvolution result for the deposited SnO film annealed at 400  $^{\circ}$ C. (d) SIMS profiles of tin and hydrogen across the 400  $^{\circ}$ C annealed SnO film. (e) AFM surface image of a 400  $^{\circ}$ C annealed SnO film. (f) AFM rms roughness values of the SnO film with various annealing temperatures.

there is a significant diffraction peak at  $30.3^{\circ}$  with some minor signals at  $35.6^{\circ}$  and  $51.0^{\circ}$ , which respectively correspond to SnO (101), SnO (101), and SnO<sub>2</sub> (211), suggesting a crystalline structure of the film after annealing. From the phase diagram of SnO<sub>2</sub>, the coexistence of SnO<sub>2</sub> and SnO phases is possible, and it is inferred that the film is mainly composed of SnO because of the relatively strong signal in the spectrum. As the annealing temperature elevates to 500 °C, the

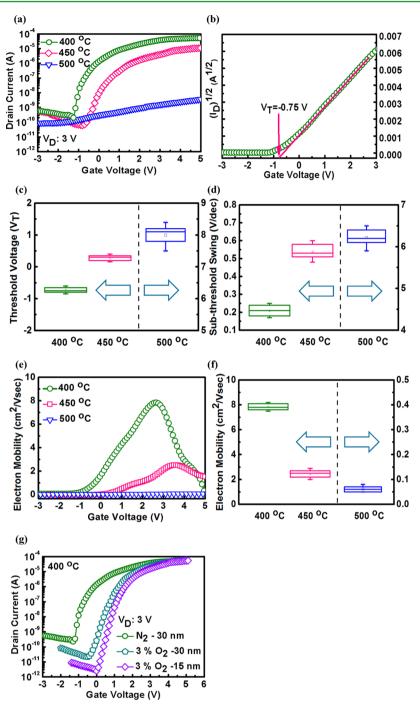

**Figure 2.** (a)  $I_D - V_G$  transfer characteristics with drain biased at 3 V for TFTs with the channel material annealed at various temperatures. (b)  $I_D^{-1/2} - V_G$  curve for TFTs processed at 400 °C. Dependence of the annealing temperature of TFTs channel material on (c) statistical variation of the threshold voltage, (d) statistical variation of the SS, (e) mobility–gate voltage characteristics, and (f) statistical variation of the peak mobility. (g) Impact of annealing ambient and channel thickness on  $I_D - V_G$  transfer characteristics for TFTs with the channel material annealed at 400 °C.

signal intensity of SnO<sub>2</sub> significantly increases while that of SnO decreases, and this implies that SnO<sub>2</sub> is the main composition of the film. The phenomenon is consistent with that reported in ref 18 and can be explained by the disproportionation reaction (SnO  $\rightarrow$  SnO<sub>2</sub> + Sn) that causes the decomposition of SnO to SnO<sub>2</sub> at higher temperature. Shown in Figure 1b are the annealing temperature-dependent O 1s spectra from XPS analysis. As the annealing temperature increases from 400 to 500 °C, the peak binding energy (BE) shifts toward higher energy, which implies that more O atoms are incorporated in SnO, and the results are consistent with

those reported in the literature.<sup>24</sup> The reason why 500 °C annealing incorporates more O atoms can be explained by the fact that, although the annealing was conducted in ambient N<sub>2</sub>, there was still residual oxygen in the ambient because it was not performed in vacuum. The inference that the 400 °C annealed film is mainly composed of SnO can be further confirmed by the XPS Sn 3d spectrum for the same sample shown in Figure 1c. It has been reported that the BE peak of Sn 3d<sub>5/2</sub> occurs at 486.1 and 486.7 eV for SnO and SnO<sub>2</sub>, respectively. From the deconvolution results, it can be clearly observed that the spectrum consists of a main SnO peak with a BE of 486.1 eV

with inclusion of a minor  $SnO_2$  peak, which is consistent with the result of XRD measurement. Besides confirming the hybrid phases with SnO and SnO<sub>2</sub> in the oxide film, XPS analysis also verifies the oxide film with an average composition ratio [O]/ [Sn] of 1.1. Note that, from the composition ratio of [O]/[Sn], density, and molecular weights of SnO<sub>2</sub> and SnO, the volume fraction of SnO<sub>2</sub> and SnO of the film is 1:9. Even though the film was deposited from the SnO<sub>2</sub> source, the formation of SnO can be explained by the lattice structures of SnO<sub>2</sub> and SnO. For SnO<sub>2</sub>, each Sn atom has six O-atom neighbors with a Sn-O bond length of 0.206 nm. On the other hand, for SnO, only four O-atom neighbors for each Sn atom with a bond length of 0.222 nm are found. Therefore, it is likely that the SnO<sub>2</sub> phase can be transformed into SnO by removing O atoms and adjusting the positions of the Sn atoms.<sup>18,25</sup> Figure 1d displays the SIMS profile of tin (Sn) and hydrogen (H) across the 400 °C annealed SnO film. It can be observed that the amount of hydrogen in SnO is negligible and comparable with that in the underlying SiO<sub>2</sub> film. Figure 1e shows the AFM surface morphology for the SnO film with 400 °C annealing, which exhibits a smooth surface with a root-mean-square (rms) roughness of 0.95 nm. The smooth SnO surface is beneficial to suppressing the charge trap at the interface between the channel and gate dielectric and alleviating the roughnessinduced leakage current and carrier mobility degradation.<sup>26,27</sup> Figure 1f demonstrates the dependence of the annealing temperature on the SnO surface roughness. As the annealing temperature increases to 500 °C, the rms roughness slightly degrades to 4.12 nm, which may be attributed to the larger grain size of the film.

With the drain voltage  $(V_{\rm D})$  and source voltage  $(V_{\rm S})$ respectively biased at 3 and 0 V, the  $I_D - V_G$  transfer characteristics for TFTs with the channel material annealed at various temperatures are shown in Figure 2a, where  $I_{\rm D}$  and  $V_{\rm G}$ respectively denote the drain current and gate-to-source voltage. For 400 and 450 °C annealing, devices display apparent transistor behavior with an ON/OFF current ratio up to  $2.5 \times 10^5$  and  $1.6 \times 10^5$ , respectively. The transistor behavior significantly degrades as the annealing increases to 500 °C. No matter what the annealing temperature is, n-type TFT behavior is found, which implies that the hybrid channel is capable of electron conduction, and this phenomenon has never been reported in the literature. Although SnO has been widely perceived as a p-type semiconductor, it was also reported that CBM of SnO is mainly formed by Sn 5p orbitals and electron transport near the CBM is possible from theoretical calculation.<sup>20</sup> In fact, it has also been reported that p-type SnO resulted from a shallow donor complex formed by hydrogen and tin vacancies.<sup>28</sup> From separate experiments in this work, p-type SnO indeed can be formed by annealing in forming gas (8% H<sub>2</sub>/92% N<sub>2</sub>) at 400 °C. However, from Halleffect measurement, the p-type film has a relatively high resistivity with a low hole concentration ( $\sim 10^{14}$  cm<sup>-3</sup>), and it requires further process optimization for TFT applications. If one can suppress hydrogen incorporation, the p-type property of SnO can be avoided. Furthermore, it is found that the SnO channel with oxygen deficiency is favorable for electron mobility.<sup>18</sup> As evidenced in Figure 1d, this is the case for the 400 °C annealed film in this work, where negligible hydrogen and only a trace amount of oxygen exist in the ambient N<sub>2</sub> annealing because of residual oxygen. That is, negligible hydrogen prevents a p-type semiconductor from occurring, while oxygen-deficient SnO in the 400 °C annealed film

provides good media for electron conduction. On the other hand, oxygen vacancies  $(V_0)$  and metal-ion interstitials are found to be the main contributors for free electrons in an ntype SnO<sub>2</sub>-based oxide semiconductor. The role that a small amount of SnO<sub>2</sub> in the hybrid film plays is to introduce a certain number of oxygen vacancies into the film. These oxygen vacancies will contribute to more donor states (free electrons), and therefore the hybrid channel reveals the property of an ntype semiconductor. At 450 °C annealing temperature, from the trend obtained in XRD analysis, a larger amount of SnO<sub>2</sub> and a smaller amount of SnO compared to that of 400 °C will be formed in the film because of disproportionation reaction. However, the change of the SnO/SnO<sub>2</sub> ratio could not explain the lower drive current. The most likely reason is modulation in the oxygen amount in the film, which changes the electron conduction behavior. Because of the residual oxygen in ambient N<sub>2</sub> annealing, a higher annealing temperature would lead to more oxygen incorporation, which would respectively deteriorate the electron conduction in SnO because the oxygen deficiency is more favorable for the mobility and decreases the electron concentration in SnO<sub>2</sub> because the number of oxygen vacancies reduces. As the annealing temperature increases to 500 °C, as indicated in XRD analysis, although SnO<sub>2</sub> becomes the main composition of the annealed film, insignificant transistor behavior is observed. This degraded performance can be ascribed to the incorporation of an even higher amount of oxygen into SnO<sub>2</sub>, which dramatically decreases the number of oxygen vacancies and consequently reduces the electron concentration, making the film a semiconductor of high resistivity. From evolution of the electrical characteristics for different annealing temperatures, it is confirmed that the annealing temperature and the amount of oxygen incorporated into the film play an essential role in determining the device performance. The aforementioned argument that the electron concentration decreases with increasing annealing temperature can be proven by the carrier concentration obtained by Halleffect measurement. From the measurement, the oxide semiconductor is indeed of the n-type property. At 400 °C annealing, the carrier concentration is  $5.5 \times 10^{19}$  cm<sup>-3</sup>, and it decreases to  $1.8 \times 10^{19} \text{ cm}^{-3}$  as the annealing temperature elevates to 450 °C. At 400 °C annealing, it seems that the number of oxygen vacancies in SnO and SnO<sub>2</sub> reaches an optimum level, and therefore the best performance is achieved. Furthermore, for 400 °C annealed devices, no ambipolar behavior is found in the transfer characteristic, which is much different from the reported SnO<sup>20</sup> and suggests better control for the off-state current. Shown in Figure 2b is the transfer curve for 400 °C annealed devices with the drain current  $(I_{\rm D})$ axis changed to  $I_D^{1/2}$ .  $V_T$  of -0.75 V can be extracted from the transfer curve presented in this form. Note that the negative  $V_{\rm T}$ indicates that the devices are of depletion-mode TFTs, which require negative gate bias to deplete the channel electrons to turn the devices off. It is worth noting that, because many ntype oxide semiconductor TFTs are of depletion mode, designing the driving circuits such as shift and level shifters that can be operated in depletion mode would be indispensable for an oxide semiconductor-based TFT display. Recently, many promising driving circuit designs have been proposed,<sup>29-31</sup> and therefore this ushers in a new era to implement depletion-mode TFTs in the driving circuits. Furthermore, it has also been reported that a TFT-based inverter with an enhancement mode driver would show higher voltage gain for a depletion load than an enhancement load,<sup>32,33</sup> which means depletion-mode

| Table 1. Comparison of the Main Device Parameters for n-Type TFTs with Various Channel Material | f the Main Device Parameters for n-Type TFTs with Vario | us Channel Materials |

|-------------------------------------------------------------------------------------------------|---------------------------------------------------------|----------------------|

|-------------------------------------------------------------------------------------------------|---------------------------------------------------------|----------------------|

| channel material               | gate dielectric                                               | mobility $(cm^2/V \cdot s)$ | SS (V/dec) | $I_{\rm ON}/I_{\rm OFF}$ | ref       |

|--------------------------------|---------------------------------------------------------------|-----------------------------|------------|--------------------------|-----------|

| hybrid of SnO/SnO <sub>2</sub> | ZrO <sub>2</sub>                                              | 7.84                        | 0.21       | $2.5 \times 10^{5}$      | this work |

| TiInZnO                        | SiO <sub>2</sub>                                              | 0.96                        | 0.7        | $2.1 \times 10^{6}$      | 2015, 2   |

| ZrInZnO                        | $SiN_x$                                                       | 3.9                         | 0.98       | $\sim 10^{7}$            | 2015, 2   |

| YInZnO                         | SiO <sub>2</sub>                                              | 4.76                        | 2.9        | $1.32 \times 10^{6}$     | 2013, 3   |

| ZnO                            | $Al_2O_3$                                                     | ~4                          | N/A        | $\sim 10^{7}$            | 2009, 7   |

| ZnO                            | $SiO_2/SiN_x$                                                 | 0.97                        | N/A        | >10 <sup>5</sup>         | 2003, 8   |

| LiZnO                          | SiO <sub>2</sub>                                              | $1.5 \times 10^{-2}$        | 0.24       | $\sim 10^{5}$            | 2014, 9   |

| GaZnO                          | $Al_2O_3$                                                     | 1.058                       | ~2.2       | $1.08 \times 10^{6}$     | 2014, 10  |

| TiO <sub>x</sub>               | SiO <sub>2</sub>                                              | 1.64                        | 1.86       | $4.7 \times 10^{5}$      | 2009, 11  |

| TiO <sub>2-x</sub>             | SiO <sub>2</sub>                                              | 0.69                        | 2.45       | $2.04 \times 10^{7}$     | 2011, 12  |

| SnO <sub>2</sub>               | Al <sub>2</sub> O <sub>3</sub> /TiO <sub>2</sub> superlattice | 0.8                         | ~4         | $\sim 10^{5}$            | 2004, 14  |

| SnO <sub>2</sub>               | SiO <sub>2</sub>                                              | 0.37                        | 2          | $\sim 10^{6}$            | 2014, 15  |

| SnO                            | SiO <sub>2</sub>                                              | $1.4 \times 10^{-3}$        | ~3.5       | $\sim 10^{2}$            | 2011, 19  |

| SnO                            | SiO <sub>2</sub>                                              | 1.02                        | ~10        | $\sim 10^{3}$            | 2012, 20  |

devices still have certain advantages for circuit application. Figure 2c shows that the statistical variation of  $V_{\rm T}$  for different annealing temperatures and  $V_{\rm T}$  shifts toward the positive direction as the annealing temperature increases. In addition to typical  $I_{\rm D} - V_{\rm G}$  characteristics,  $I_{\rm D} - V_{\rm G}$  hysteresis is important as well because it is an important indicator of dielectric bulk traps and the interfacial quality between ZrO<sub>2</sub> and the SnO/SnO<sub>2</sub> hybrid channel, and the results (not shown) for different annealing temperatures show that hysteresis for 400 °C annealed devices is 0.35 V and hysteresis deteriorates with the annealing temperature. The small hysteresis of 400 °C annealed devices implies either good interfacial quality or few dielectric bulk traps. Shown in Figure 2d are the SS for devices with various annealing temperatures. With  $V_{\rm D}$  biased at 3 V, the SS for 400 °C annealed devices is 0.21 V/dec, and the value degrades to 0.52 V/dec as the annealing temperature increases to 450 °C. The degradation is partly ascribed to the worse interfacial quality, as evidenced by the hysteresis value. It is worth mentioning that the steep SS of 0.21 V/dec for 400 °C annealed devices is superior to that of many binary oxide-based TFTs such as Ga-doped  $ZnO_{,}^{10}$  Ti $O_{,2}^{11,12}$  SnO $_{,2}^{14,15}$  SnO $_{,2}^{19,20}$ and even InZnO-based oxides such as ZrInZnO,<sup>2</sup> TiInZnO<sup>2</sup>, and YInZnO.<sup>3</sup> Note that the operation voltage of 3 V in this work is much lower than that of ZrInZnO,<sup>2</sup> TiInZnO,<sup>2</sup> YInZnO<sup>,3</sup> LiZnO<sup>,9</sup> TiO<sub>x</sub>-based,<sup>11-13</sup> SnO<sub>2</sub><sup>14,15</sup> and ZnO<sup>8</sup> ntype TFTs, which require voltages higher than 20 V. The low operation voltage is primarily due to the adoption of high- $\kappa$ (high dielectric constant) ZrO2, which leads to stronger channel control from the gate. The desirable SS also leads to high electron mobility, which is shown in Figure 2e,f, mobility versus gate voltage characteristics, and statistical variation of the peak mobility for different annealing temperatured. Note that the mobility  $(\mu)$  was extracted for TFTs operated in the linear region by the equation  $\mu = (\partial I_D / \partial V_G) (L/W) (1/C_{ox}) (1/V_{DS})$ , where L and W respectively denote the channel length and width, while  $C_{ox}$  is the capacitance per unit area. For 400 °C annealed devices, by considering the gate current effect on the drain current, the mobility can be as high as 7.84 cm<sup>2</sup>/V·s, which outperforms undoped binary oxides such as  $TiO_{x}^{11,12}$   $SnO_{2}^{14,15}$   $SnO_{1}^{19,20}$  and  $ZnO_{7}^{7,8}$  doped binary oxides such as LiZnO<sup>9</sup> and GaZnO,<sup>10</sup> or even InZnO-based oxides such as ZrInZnO,<sup>2</sup> TiInZnO<sup>2</sup>, and YInZnO.<sup>3</sup> Note that the reported mobility for n-type SnO ranges from  $1.4 \times 10^{-3}$  to  $1.02 \text{ cm}^2/\text{V}$ . s,<sup>19,20</sup> which may arise from the relatively oxygen-rich nature of the oxide film.<sup>20</sup> Table 1 summarizes the main electrical

characteristics of n-type TFTs formed on various channel materials. Considering the overall performance and process complexity, the SnO/SnO<sub>2</sub> hybrid channel gated by the ZrO<sub>2</sub> dielectric indeed holds the potential to realize high-performance TFTs in a more economic approach. Note that a high ON/OFF current ratio is desirable for TFT devices and there is still room to enhance the ratio of 400 °C annealed devices. In fact, from separate experiments, the mechanical stress between ZrO<sub>2</sub> and SnO is measured to be -0.04 GPa from a laser curvature method, which is based on variation of the characteristic curvature radius of the sample before and after ZrO<sub>2</sub> deposition. The stress is so small that it is not the main reason for the unsatisfactory ON/OFF current ratio. The most likely reason is the high OFF-state current ( $I_{OFF}$ ), which may have resulted from the following factors.

# 1. HIGH CONDUCTIVE CHANNEL

The channel contains a large number of oxygen vacancies and, consequently, a high carrier concentration in the channel material. It is the high carrier concentration that makes the device difficult to be completely depleted, and therefore high  $I_{\text{OFF}}$  is observed. By moderation of the number of oxygen vacancies in the channel through additional annealing in oxygen-containing ambient such as wet air,<sup>34</sup> further improved I<sub>OFF</sub> may be achieved. From our preliminary experimental results, as shown in Figure 2g, by annealing the channel material at 400 °C in N2 ambient with 3% oxygen, the TFTs demonstrated  $I_{\rm OFF}$  of 2.1  $\times$  10<sup>-11</sup> A/cm<sup>2</sup>, which is lower than that from N<sub>2</sub> annealing at the same temperature by nearly 1 order of magnitude, with the ON-state current  $(I_{ON})$  kept almost unchanged. Therefore, the  $I_{\rm ON}/I_{\rm OFF}$  ratio enhances to  $2.8 \times 10^{\circ}$ . Although there is still room to further improve the ratio, annealing the channel material in oxygen-containing ambient indeed provides an alternative direction. A more indepth study in this direction will be reported elsewhere. Besides the reduced  $I_{OFF}$ , the other important observation is that devices annealed in the ambient with 3% oxygen incorporation also display a positive  $V_{\rm T}$  shift from -0.75 to 0.88 V, indicating the change of the operation mode from depletion to enhancement, which would provide more flexibility in circuit design. The behavior of  $I_{\rm OFF}$  reduction as well as the change of the operation mode can be explained by modulation of the number of oxygen vacancies in the channel.

## 2. HIGH GATE LEAKAGE CURRENT

It has been reported<sup>35</sup> that, for depletion-mode TFTs,  $I_{OFF}$  includes not only leakage from the channel, as mentioned in part 1, but also the gate leakage current. In this work, the gate leakage current for 400 °C annealed TFTs at -1 V is comparable with the drain current at the same bias and it indeed has room to suppress the gate leakage to improve  $I_{OFF}$ . Further reduced gate leakage current is expected by adopting appropriate surface passivation for the hybrid channel to enhance the bonding structure between  $ZrO_2$  and the channel material and employing additional annealing on  $ZrO_2$  to strengthen the bonding structure in the oxide bulk.

#### 3. THICK CHANNEL MATERIAL

High I<sub>OFF</sub> is observed if the channel is difficult to deplete. Besides the high carrier concentration of the channel, the relatively thick channel thickness also makes the channel difficult to completely deplete,<sup>32</sup> which is the case in this work because the channel thickness is 30 nm. On the basis of the aforementioned result that TFTs processed at 400  $^\circ C$  in ambient N<sub>2</sub> with 3% oxygen exhibit a better  $I_{ON}/I_{OFF}$  ratio than pure N2 annealing, devices with the same annealing conditions but with a thinner channel thickness of 15 nm were fabricated and investigated. The  $I_{\rm D}-V_{\rm G}$  transfer characteristic was demonstrated in Figure 2g. As expected, compared to those with a channel thickness of 30 nm, devices with a 15 nm channel thickness exhibit lower  $I_{\text{OFF}}$ , comparable  $I_{\text{ON}}$ , and higher  $I_{\rm ON}/I_{\rm OFF}$  ratio of 2.2 × 10<sup>7</sup>. The improved  $I_{\rm ON}/I_{\rm OFF}$  ratio for the decreased channel thickness can be explained by the reduced bulk conduction and therefore lower IOFF, which is consistent with the results reported in the literature.<sup>32,36,37</sup> In addition, a positive shift of  $V_{\rm T}$  can also be observed for those with thinner channel thickness. Given that the free electron concentration is constant in the channel layer with different thicknesses, the total number of free electrons is proportional to the channel thickness. For devices with thinner channel thickness, the decreased number of free electrons requires a less negative bias to turn off the drain current in  $\hat{\mathrm{TFTs}},^{32}$  and therefore the positive shift of  $V_{\rm T}$  is obtained.

From the aforementioned physical and electrical characteristics, the competitive advantages of the hybrid phase SnO channel over other n-type oxide semiconductor TFTs are summarized below. (1) From a process point of view, the hybrid phase channel is based on a binary oxide without doping or employing a multicomponent oxide semiconductor that simplifies the process complexity and makes it a productionworthy process. (2) From an electrical performance point of view, the n-type ZrO2-gated hybrid phase TFTs reveal advantages over previous studies in terms of a small operation voltage of 3 V, which is much lower than those reported in the literature, a higher electron mobility of 7.84 cm<sup>2</sup>/V·s, which outperforms most binary oxide semiconductor-based TFTs reported in the literature, a low SS of 0.21 V/dec, which is superior to most oxide semiconductor-based TFTs because of the employment of a high- $\kappa$  dielectric. (3) From a circuit application point of view, the operation mode of the hybrid phase devices can be modulated from the depletion mode with annealing in ambient N2 to the enhancement mode with annealing in ambient N2 incorporated with 3% oxygen, both at 400 °C annealing. The results are very promising for circuit application because it is possible to fabricate both depletion and enhancement mode devices on the same wafer to implement

inverters, with the enhancement one for the driver and the depletion one for the load. As aforementioned statements, the circuit configuration would result in a larger voltage gain than the enhancement load. That is, the hybrid phase channel proposed in this work exhibits the possibility of forming n-type depletion mode TFTs and n-type enhancement mode TFTs through appropriate annealing. Even though the latter devices are not comprehensively investigated, the hybrid phase channel indeed holds great potential to provide available choices for actual device and circuit integration.

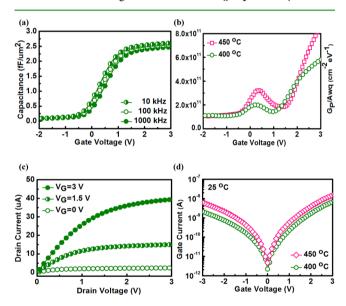

Compared to other oxide semiconductor TFTs, the much improved mobility of the TFT channel material processed at 400 °C in this work can be attributed to the good current conduction media of the oxide film and the steep SS. The former resulted from the oxygen-deficient oxide film that makes both SnO and SnO<sub>2</sub> favorable for current conduction, while the latter can be ascribed to the large gate capacitance and low  $D_{it}$  between  $ZrO_2$  and the hybrid channel. The large gate capacitance can be confirmed by the C-V measurement, which is shown in Figure 3a, while low  $D_{it}$  is proven by the G-

**Figure 3.** Electrical characteristics for TFTs with channel material annealed at 400 °C. (a) C-V curves measured at different frequencies. (b) G-V curve obtained at 100 kHz. (c)  $I_D-V_{DS}$  output characteristics. (d) Gate leakage performance for the same device measured at 25 °C. G-V and gate leakage for TFTs processed at 450 °C are also shown in parts b and d.

V characteristic measured at 100 kHz, which is shown in Figure 3b. Figure 3a exhibits the C-V curves measured at different frequencies ranging from 10 to 1000 kHz. For the C-Vmeasurement, alternating-current impedance between the gate and source was measured by applying a small signal voltage with a sweep voltage on the gate terminal. Because the gate terminal is positively biased, TFT is under the accumulation region and the measured capacitance is  $C_{ox}$  in series with  $C_{B}$ , where  $C_{ox}$  is the capacitance from the gate dielectric while  $C_{B}$  is the capacitance due to gate voltage-responsive total charge in the active film. Because  $C_{\rm B}$  is much larger than  $C_{\rm ox}$ , the measured capacitance under accumulation is mainly determined by  $C_{ox}^{38}$  A maximum capacitance occurring at the positive gate voltage suggests that the hybrid channel has n-type semiconductor nature. From the measured capacitance at a gate voltage of 3 V with a measurement frequency of 100 kHz, the

#### **ACS Applied Materials & Interfaces**

CET of annealed ZrO<sub>2</sub> was extracted to be 13.5 nm with a  $\kappa$ value of 17.3. In addition, the small frequency dispersion in the depletion region implies the desirable interfacial quality between the dielectric and hybrid channels. From the G-Vcharacteristic shown in Figure 3b, the interfacial quality can be further quantified by the  $D_{it}$  value of 5.16  $\times$  10<sup>11</sup> cm<sup>-2</sup> eV<sup>-1</sup>, which means the trap density per unit energy in the band gap of the channel material, and it can be estimated from the peak value in the G-V curve by the formula  $D_{\rm it} \sim 2.5 G_{\rm p,max}/A\omega q$ , where  $G_{\rm p}$ , A, and  $\omega$  respectively denote the parallel conductance peak, device area, and angular frequency.<sup>39</sup> In fact, from the SS value, the total trap density  $(N_t)$ , which includes both the density of deep bulk states in the channel  $(N_{\text{bulk}})$  and interface states between the channel/gate dielectric  $(N_{\rm it})$ , can also be extracted by the formula  $N_{\rm t} = N_{\rm bulk} + N_{\rm it} =$  $[SS \log(e)q/k_BT - 1](C_{ox}/q)$ , where e is Euler's number (irrational constant), k is the Boltzmann constant, T is the absolute temperature, and q is the charge of an electron.<sup>40</sup> From the measured data,  $N_t$  is found to be  $3.92 \times 10^{12}$  cm<sup>-2</sup>. There is still room to reduce the  $N_t$  value to achieve a higher device performance. For interface states, it can be further improved by adopting appropriate surface passivation for the hybrid channel or additional thermal treatment to enhance the bonding structure between ZrO<sub>2</sub> and the channel material. For bulk states in the channel, assuming that the trap density per area is constant, it may be improved by using a thinner channel thickness, which is still under investigation. Also shown in Figure 3b is the G-V characteristic for TFTs processed at 450 °C. From the peak value, its  $D_{it}$  is extracted to be  $8.52 \times 10^{11}$ cm<sup>-2</sup> eV<sup>-1</sup>, which is higher than that of 400 °C annealed TFTs and may arise from a rougher surface. The higher  $D_{it}$  value is consistent with the larger hysteresis, and it also partly explains the worse SS performance and inferior mobility. Figure 3c displays the output characteristics for devices with 400 °C annealing. The devices demonstrate obvious pinch-off voltage and current saturation. It can be clearly seen that the operating voltage can be as low as 3 V, which is essential for green electronics. Figure 3d shows the gate current  $(I_G)-V_G$  curve measured at 25 °C for TFTs processed at 400 and 450 °C. At  $V_{\rm G}$  of 3 V, which corresponds to the ON state, a gate leakage current of  $1.4 \times 10^{-8}$  A is obtained for 450 °C annealed TFTs, and the current improves to  $6.8 \times 10^{-9}$  A as the annealing temperature lowers to 400 °C. The improved leakage current performance can be ascribed to lower  $D_{it}$  and a smoother dielectric/channel interface. Obviously, the current at positive bias is higher than that at negative bias. The asymmetric current level for different bias polarities also implies the n-type semiconductor property of the channel because it is under the accumulation regime at positive bias.

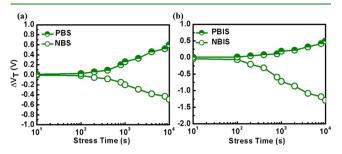

Besides understanding the electrical behavior of the  $ZrO_2$ gated TFTs formed on the SnO/SnO<sub>2</sub> hybrid channel, reliability assessment for the devices is important as well to ensure its feasibility for practical applications. Related reliability assessment conducted under ON and OFF states was studied. Because bias stress in the dark environment is not a significant issue, therefore the reliability under illumination either for a positive or a negative gate bias was also evaluated. To address the issue, with  $V_D$  fixed at +6 V,  $V_G$  of -13.5 and +13.5 V are respectively applied on the gate to evaluate its  $V_T$  instability under OFF (negative bias stress, NBS) and ON (positive bias stress, PBS) states in the dark environment. For assessment of the negative bias illumination stress (NBIS) and positive bias illumination stress (PBIS), a blue-light-emitting diode with a wavelength of 430 nm and a power density of  $0.1 \text{ mW/cm}^2$  was adopted for the reliability test. Parts a and b of Figure 4

**Figure 4.** Impact of the gate bias stress time on  $V_T$  instability with a high gate voltage of ±13.5 V under (a) dark and (b) illumination environments measured at 25 °C.

respectively demonstrate the NBS/PBS and NBIS/PBIS results for 400 °C annealed devices. The  $V_{\rm T}$  shift for NBS is -0.49 V after 10<sup>4</sup> s of stress, and the data are comparable with those for PBS. The results confirm that  $V_{\rm T}$  instability is not a critical issue in the dark environment. In contrast, under the illumination of blue light, the  $V_{\rm T}$  shift for NBIS degrades to -1.29 V after  $10^4$  s of stress, while the result for PBIS becomes slightly better than PBS after the same stress. The remarkable difference between NBIS and PBIS can be explained as follows. In the hybrid phase channel, oxygen vacancies  $(V_0)$  locate in the band gap of the SnO film. Under illumination, because of the high photoenergy from blue light, electrons in the valence band maximum (VBM) can be excited to the energy states of the  $V_{0}$ , and the process leaves holes at the VBM. Because the negative bias continues to apply on the gate, the induced holes will be trapped at the interface between the gate dielectric and channel material and/ or the bulk region of the gate dielectric because of the favorable electric field and consequently band bending.<sup>41</sup> As the amount of trapped holes increases,  $V_{\rm T}$  shift toward the negative direction can be observed. For PBIS, the slightly improved  $V_{\rm T}$ shift compared to that of PBS can be ascribed to electron derapping from the gate dielectric with illumination and therefore the  $V_{\rm T}$  shift becomes less pronounced.<sup>42</sup>

In conclusion, an undoped oxide semiconductor with hybrid phases of SnO/SnO<sub>2</sub> was explored as the channel material for n-type TFTs. At 400 °C annealing, the channel is composed of a small amount of SnO<sub>2</sub> inclusion in the SnO film, and an optimum number of oxygen vacancies were introduced into the oxide film, making both SnO and SnO<sub>2</sub> favorable for current conduction. Several promising electrical characteristics in terms of a high electron mobility of 7.84 cm<sup>2</sup>/V·s, a steep SS of 0.21 V/dec, a large ON/OFF current ratio up to  $2.5 \times 10^5$ , a small  $D_{\rm it}$  value of 5.16  $\times$  10<sup>11</sup> cm<sup>-2</sup> eV<sup>-1</sup>, and a low gate leakage current were obtained for the ZrO2-gated TFTs operated at a voltage of 3 V. Upon integration of 3% oxygen annealing with a thinner channel thickness, TFTs with even higher  $I_{\rm ON}/I_{\rm OFF}$ ratios exceeding 107 can also be obtained. A good reliability performance is also evidenced by the relatively stable SS and  $V_{\rm T}$ under high voltage stress. Compared to other n-type oxide semiconductors, the overall performance of the undoped hybrid channel devices suggests that it holds the potential to empower advanced low-power/high-performance TFTs. Most importantly, the hybrid channel proves the feasibility to achieve high electron mobility in a SnO-based oxide semiconductor and paves a possible avenue to implement depletion/enhancement TFTs and even CMOS TFTs by a single material.

# AUTHOR INFORMATION

## **Corresponding Author**

\*E-mail: yunhwu@mx.nthu.edu.tw.

## **Author Contributions**

The manuscript was written through contributions of all authors. All authors have given approval to the final version of the manuscript.

#### Notes

The authors declare no competing financial interest.

# ACKNOWLEDGMENTS

This work was supported by the Ministry of Science and Technology of Taiwan under Contracts NSC 101-2628-E-007-012-MY3 and NSC 101-2120-M-009-004.

#### REFERENCES

(1) Nomura, K.; Ohta, H.; Takagi, A.; Kamiya, T.; Hirano, M.; Hosono, H. Room-Temperature Fabrication of Transparent Flexible Thin-Film Transistors Using Amorphous Oxide Semiconductors. *Nature* **2004**, *432*, 488–492.

(2) Kwon, J. Y.; Jeong, J. K. Recent Progress in High Performance and Reliable N-Type Transition Metal Oxide-Based Thin Film Transistors. *Semicond. Sci. Technol.* **2015**, *30*, 024002.

(3) Ting, C. C.; Chang, S. P.; Li, W. Y.; Wang, C. H. Enhanced Performance of Indium Zinc Oxide Thin Film Transistor by Yttrium Doping. *Appl. Surf. Sci.* 2013, 284, 397–404.

(4) Ryu, M. K.; Yang, S.; Park, S. H. K.; Hwang, C. S.; Jeong, J. K. High Performance Thin Film Transistor with Co-sputtered Amorphous Zn-In-Sn-O Channel: Combinatorial Approach. *Appl. Phys. Lett.* **2009**, *95*, 072104.

(5) Yang, B. S.; Huh, M. S.; Oh, S.; Lee, U. S.; Kim, Y. J.; Oh, M. S.; Jeong, J. K.; Hwang, C. S.; Kim, H. J. Role of ZrO<sub>2</sub> Incorporation in the Suppression of Negative Bias Illumination-Induced Instability in Zn-Sn-O Thin Film Transistors. *Appl. Phys. Lett.* **2011**, *98*, 122110.

(6) Fortunato, E. M. C.; Barquinha, P. M. C.; Pimentel, A. C. M. B. G.; Gonçalves, A. M. F.; Marques, A. J. S.; Martins, R. F. P.; Pereira, L. M. N. Wide-Bandgap High-Mobility ZnO Thin-Film Transistors Produced at Room Temperature. *Appl. Phys. Lett.* **2004**, *85*, 2541–2543.

(7) Park, S. H. K.; Hwang, C. S.; Ryu, M.; Yang, S.; Byun, C.; Shin, J.; Lee, J. L.; Lee, K.; Oh, M. S.; Im, S. Transparent and Photo-Stable ZnO Thin-film Transistors to Drive an Active Matrix Organic-Light-Emitting-Diode Display Panel. *Adv. Mater.* **2009**, *21*, 678–682.

(8) Masuda, S.; Kitamura, K.; Okumura, Y.; Miyatake, S.; Tabata, H.; Kawai, T. Transparent Thin Film Transistors Using ZnO as an Active Channel Layer and Their Electrical Properties. *J. Appl. Phys.* **2003**, *93*, 1624–1630.

(9) Jeon, H. J.; Lee, S. G.; Kim, H.; Park, J. S. Enhanced Mobility of Li-Doped ZnO Thin Film Transistors Fabricated by Mist Chemical Vapor Deposition. *Appl. Surf. Sci.* **2014**, *301*, 358–362.

(10) Nam, T.; Lee, C. W.; Kim, H. J.; Kim, H. Growth Characteristics and Properties of Ga-Doped ZnO (GZO) Thin Films Grown by Thermal and Plasma-Enhanced Atomic Layer Deposition. *Appl. Surf. Sci.* **2014**, *295*, 260–265.

(11) Park, J. W.; Lee, D.; Kwon, H.; Yoo, S.; Huh, Y. Performance Improvement of N-Type  $TiO_x$  Active-Channel TFTs Grown by Low-Temperature Plasma-Enhanced ALD. *IEEE Electron Device Lett.* **2009**, 30, 739–741.

(12) Choi, K. H.; Kim, H. K. Fabrication of Transparent  $TiO_{2-x}$ Channel-Based Thin Film Transistors Using an Oxygen-Deficient  $TiO_{2-x}$  Target. *Electrochem. Solid-State Lett.* **2011**, *14*, H314.

(13) Oike, G.; Yajima, T.; Nishimura, T.; Nagashio, K.; Toriumi, A. High Electron Mobility (>16 cm<sup>2</sup>/Vsec) FETs with High On/Off Ratio (>10<sup>6</sup>) and Highly Conductive Films ( $\sigma$ >10<sup>2</sup> S/cm) by Chemical Doping in Very Thin (~20 nm) TiO<sub>2</sub> Films on Thermally Grown SiO<sub>2</sub>. *Proc. IEEE IEDM* **2013**, 300–303.

(14) Presley, R. E.; Munsee, C. L.; Park, C.-H.; Hong, D.; Wager, J. F.; Keszler, D. A. Tin Oxide Transparent Thin-Film Transistors. *J. Phys. D: Appl. Phys.* **2004**, *37*, 2810–2813.

(15) Zhai, J.; Zhang, X.; Hai, F.; Yu, X.; Zhu, R.; Zhang, W. Fabrication and Characterization of Thin-Film Transistors with SnO<sub>2</sub> Channel by Spray Pyrolysis. *Jpn. J. Appl. Phys.* **2014**, *53*, 066506.

(16) Sun, J.; Lu, A.; Wang, L.; Hu, Y.; Wan, Q. High-Mobility Transparent Thin-Film Transistors with an Sb-Doped  $SnO_2$  Nanocrystal Channel Fabricated at Room Temperature. *Nanotechnology* **2009**, *20*, 335204.

(17) Dattoli, E. N.; Wan, Q.; Guo, W.; Chen, Y.; Pan, X.; Lu, W. Fully Transparent Thin-Film Transistor Devices Based on  $SnO_2$  Nanowires. *Nano Lett.* **2007**, *7*, 2463–2469.

(18) Liang, L. Y.; Liu, Z. M.; Cao, H. T.; Yu, Z.; Shi, Y. Y.; Chen, A. H.; Zhang, H. Z.; Fang, Y. Q.; Sun, X. L. Phase and Optical Characterizations of Annealed SnO Thin Films and Their p-Type TFT Application. *J. Electrochem. Soc.* **2010**, *157*, H598.

(19) Nomura, K.; Kamiya, T.; Hosono, H. Ambipolar Oxide Thin-Film Transistor. *Adv. Mater.* **2011**, *23*, 3431–3434.

(20) Yan Liang, L.; Tao Cao, H.; Bo Chen, X.; Min Liu, Z.; Zhuge, F.; Luo, H.; Li, J.; Cheng Lu, Y.; Lu, W. Ambipolar Inverters Using SnO Thin-Film Transistors with Balanced Electron and Hole Mobilities. *Appl. Phys. Lett.* **2012**, *100*, 263502.

(21) Hosono, H.; Ogo, Y.; Yanagi, H.; Kamiya, T. Bipolar Conduction in SnO Thin Films. *Electrochem. Solid-State Lett.* **2011**, *14*, H13.

(22) Kwoka, M.; Ottaviano, L.; Koscielniak, P.; Szuber, J. XPS, TDS, and AFM Studies of Surface Chemistry and Morphology of Ag-Covered L-CVD SnO<sub>2</sub> Nanolayers. *Nanoscale Res. Lett.* 2014, *9*, 260.

(23) Ristoscu, C.; Cultrera, L.; Dima, A.; Perrone, A.; Cutting, R.; Du, H. L.; Busiakiewicz, A.; Klusek, Z.; Datta, P. K.; Rose, S. R. SnO<sub>2</sub> Nanostructured Films Obtained by Pulsed Laser Ablation Deposition. *Appl. Surf. Sci.* 2005, 247, 95–100.

(24) Kwoka, M.; Ottaviano, L.; Passacantando, M.; Santucci, S.; Czempik, G.; Szuber, J. XPS Study of the Surface Chemistry of L-CVD SnO<sub>2</sub> Thin Films after Oxidation. *Thin Solid Films* **2005**, *490*, 36–42.

(25) Liang, L. Y.; Liu, Z. M.; Cao, H. T.; Pan, X. Q. Microstructural, Optical, and Electrical Properties of SnO Thin Films Prepared on Quartz via a Two-Step Method. *ACS Appl. Mater. Interfaces* **2010**, *2*, 1060–1065.

(26) Zhang, L.; Li, J.; Zhang, X. W.; Jiang, X. Y.; Zhang, Z. L. High Performance ZnO-Thin-Film Transistor with Ta<sub>2</sub>O<sub>5</sub> Dielectrics Fabricated at Room Temperature. *Appl. Phys. Lett.* 2009, *95*, 072112.

(27) Jang, K.; Raja, J.; Kim, J.; Park, C.; Lee, Y.-J.; Yang, J.; Kim, H.; Yi, J. Bias-Stability Improvement Using Al<sub>2</sub>O<sub>3</sub> Interfacial Dielectrics in A-InSnZnO Thin-Film Transistors. *Semicond. Sci. Technol.* 2013, *28*, 085015.

(28) Varley, J. B.; Schleife, A.; Janotti, A.; Van De Walle, C. G. Ambipolar Doping in SnO. *Appl. Phys. Lett.* **2013**, *103*, 082118.

(29) Kim, B.; Cho, H. N.; Choi, W. S.; Kuk, S. H.; Yoo, J. S.; Yoon, S. Y.; Jun, M.; Hwang, Y. K.; Han, M. K. A Novel Depletion-Mode a-IGZO TFT Shift Register with a Node-Shared Structure. *IEEE Electron Device Lett.* **2012**, *33*, 1003–1005.

(30) Song, E.; Nam, H. Low Power Programmable Shift Register with Depletion Mode Oxide TFTs for High Resolution and High Frame Rate AMFPDs. *J. Disp. Technol.* **2014**, *10*, 862–866.

(31) Song, E.; Kang, B.; Han, I.; Oh, K.; Kim, B.; Nam, H. Depletion Mode Oxide TFT Shift Register for Variable Frame Rate AMOLED Displays. *IEEE Electron Device Lett.* **2015**, *36*, 247–249.

(32) Lee, J. M.; Cho, I. T.; Lee, J. H.; Kwon, H. I. Full-Swing InGaZnO Thin Film Transistor Inverter with Depletion Load. *Jpn. J. Appl. Phys.* **2009**, *48*, 100202.

(33) Baher, H. Signal Processing and Integrated Circuits, 1st ed.; John Wiley & Sons, Ltd.: New York, 2012; pp 295–298.

(34) Seo, S. J.; Hwang, Y. H.; Bae, B. S. Postannealing Process for Low Temperature Processed Sol-Gel Zinc Tin Oxide Thin Film Transistors. *Electrochem. Solid-State Lett.* **2010**, *13*, H357–H359.

(35) Zhou, F.; Yeh, B. S.; Archila, K. A.; Wager, J. F. Mobility Assessment of Depletion-Mode Oxide Thin-Film Transistors Using

## **ACS Applied Materials & Interfaces**

the Comprehensive Depletion-Mode Model. ECS J. Solid State Sci. Technol. 2014, 3, Q3027-Q3031.

(36) Dhananjay; Cheng, S. S.; Yang, C. Y.; Ou, C. W.; Chuang, Y. C.; Wu, M. C.; Chu, C. W. Dependence of Channel Thickness on The Performance of  $In_2O_3$  Thin Film Transistors. *J. Phys. D: Appl. Phys.* **2008**, 41, 092006.

(37) Jeong, J.; Hong, Y. Debye Length and Active Layer Thickness-Dependent Performance Variations of Amorphous Oxide-Based TFTs. *IEEE Trans. Electron Device* **2012**, *59*, 710–714.

(38) Lee, S.; Jeon, Y. W.; Kim, S.; Kong, D.; Kim, D. H.; Kim, D. M. Comparative Study of Quasi-Static and Normal Capacitance-Voltage Characteristics in Amorphous Indium-Gallium-Zinc-Oxide Thin Film Transistors. *Solid-State Electron.* **2011**, *56*, 95–99.

(39) Wu, Y. H.; Wu, M. L.; Lyu, R. J.; Wu, J. R.; Chen, L. L.; Lin, C. C. Crystalline  $ZrO_2$ -Gated Ge Metal-Oxide-Semiconductor Capacitors Fabricated on Si Substrate with  $Y_2O_3$  as Passivation Layer. *Appl. Phys. Lett.* **2011**, *98*, 203502.

(40) Cho, E. N.; Kang, J. H.; Yun, I. Effects of Channel Thickness Variation on Bias Stress Instability of InGaZnO Thin-Film Transistors. *Microelectron. Reliab.* **2011**, *51*, 1792–1795.

(41) Park, M. J.; Bak, J. Y.; Choi, J. S.; Yoon, S. M. Channel Composition Effect on the Bias-Illumination-Stress Stability of Solution-Processed Transparent Oxide Thin-Film Transistors Using Amorphous Aluminum-Indium-Zinc-Oxide Channel Layers. *ECS J. Solid State Sci. Technol.* **2014**, *3*, Q3005–Q3011.

(42) Chen, T. C.; Chang, T. C.; Tsai, C. T.; Hsieh, T. Y.; Chen, S. C.; Lin, C. S.; Hung, M. C.; Tu, C. H.; Chang, J. J.; Chen, P. L. Behaviors of InGaZnO Thin Film Transistor under Illuminated Positive Gate-Bias Stress. *Appl. Phys. Lett.* **2010**, *97*, 112104.